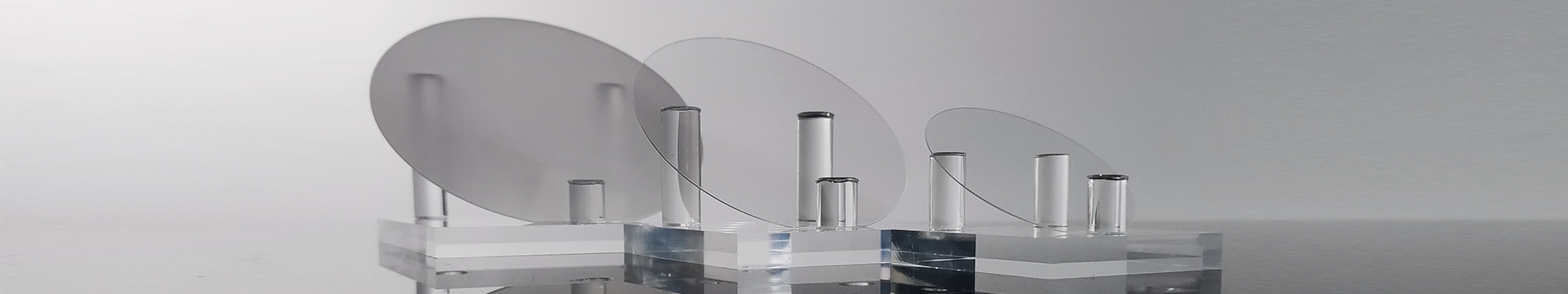

(Single-Crystal, Polycrystalline, and Diamond Films)

Diamond has emerged as an ideal thermal management substrate for heterogeneous integration with wide bandgap semiconductors such as GaN and SiC, thanks to its ultra-high thermal conductivity (exceeding 2000 W/m·K), excellent chemical inertness, and wide bandgap properties.

Among various integration approaches, wafer bonding is the most critical and scalable pathway to combine diamond substrates with semiconductor devices.

The surface flatness—typically characterized by Total Thickness Variation (TTV) and Warp—and surface roughness, commonly measured by arithmetic average roughness (Ra), play a decisive role in wafer bonding yield, interfacial strength, thermal resistance, and long-term electrical stability.

This article systematically analyzes how surface processing characteristics of single-crystal diamond, polycrystalline diamond, and diamond films affect downstream wafer bonding processes.

1. Key Surface Quality Metrics for Diamond Substrates and Process Control Ranges

Wafer bonding imposes extremely stringent requirements on diamond substrate surface quality. The most critical parameters include

surface roughness (Ra) and

flatness (TTV and Warp). Due to differences in crystal structure, each diamond type presents unique challenges and achievable control ranges.

Single-Crystal Diamond

Typical surface process: Laser trimming + mechanical machining + Chemical Mechanical Polishing (CMP)

Roughness (Ra):

Mass production: < 1 nm

Customized applications: ≤ 0.5 nm

Flatness:

TTV ≤ 10 µm, Warp ≤ 10 µm (2-inch wafer)

Key challenges:

Extreme hardness leads to low CMP efficiency; a delicate balance between polishing rate and subsurface damage is required.

Polycrystalline Diamond

Typical surface process: Dynamic Plasma Polishing (DPP) + proprietary chemical polishing

Roughness (Ra):

1–2 inch: < 1 nm (down to < 0.5 nm achievable)

3–4 inch: < 2 nm

Flatness:

2-inch wafers: Warp ≤ 10 µm

Large-area flatness control becomes significantly more difficult

Key challenges:

Numerous grain boundaries and non-uniform stress distribution cause irregular pits and protrusions, making global uniform polishing difficult.

Typical surface process: Microwave Plasma CVD (MPCVD) + plasma-assisted polishing

Roughness (Ra):

High-quality films: ≤ 0.5 nm

Standard films: < 1 nm

Thickness uniformity:

± 0.1 µm to prevent film warpage and delamination

Key challenges:

Trade-off between deposition rate and crystal quality; high carbon concentration increases surface roughness, while non-diamond phases degrade polishing efficiency.

2. Influence of Diamond Surface Quality on Wafer Bonding Performance

2.1 Single-Crystal Diamond: Ideal for High-Precision Bonding

With a perfect crystal lattice and no grain boundaries,

single-crystal diamond can achieve near-atomic-level smoothness after CMP. Its impact on wafer bonding mainly lies in

precision control and cost efficiency.

For

surface-activated bonding (SAB), a surface quality of

Ra ≤ 0.5 nm and TTV ≤ 10 µm ensures uniform activation during argon ion beam treatment. After removing native oxides, a dense bonding interface can be formed at room temperature with bonding pressure around

10 MPa, achieving

interfacial thermal resistance below 10 m²·K/GW.

If Ra exceeds 1 nm, ion beam activation may cause localized over-etching, increasing surface roughness and leaving residual interfacial voids. Excessive flatness deviation also leads to non-uniform pressure distribution, creating thermal and electrical bottlenecks.

Advantages:

Excellent surface uniformity, ideal for ≤ 2-inch wafers and high-end applications such as

5G/6G RF devices and quantum sensors.

Limitations:

High cost and difficulty in growing large-area single-crystal diamond restrict wafer-scale adoption.

2.2 Polycrystalline Diamond: Flatness as the Yield Bottleneck for Large Wafers

Polycrystalline diamond offers

lower cost and larger wafer sizes, but its surface quality poses greater challenges for wafer bonding due to grain boundaries and internal stress.

Unoptimized surfaces may exhibit peak heights up to

15 nm, resulting in bonding yields below 50%. After DPP optimization, reducing peak height to

~1.2 nm and Ra to

0.29 nm, room-temperature SAB between

thick GaN (~370 µm) and

polycrystalline diamond (~660 µm) has achieved bonding yields of

92.4%, withstanding thermal cycling from

–55°C to 250°C.

However, for wafers ≥ 3 inches, global uniformity becomes difficult. Edge warpage and roughness deviations cause stress concentration, potentially leading to film cracking. Grain boundary defects can also increase interface state density during post-bond annealing, requiring

amorphous silicon nano-buffer layers to mitigate thermal expansion mismatch.

Current applications:

Small-batch adoption in

automotive power electronics and industrial power modules, where mid-range thermal performance is sufficient.

2.3 Diamond Films: Synergistic Control of Roughness and Thickness Uniformity

Diamond films are typically deposited on

Si or SiC substrates via CVD. Their bonding performance depends on both

surface roughness and

film-substrate adhesion strength.

Using MPCVD with

CH₄ concentration below 5% and argon introduction to refine grain size, diamond films with

Ra ≤ 0.5 nm can be achieved. Combined with plasma-assisted polishing, these films meet the stringent requirements of both

surface-activated bonding and hydrophilic bonding.

When bonded to GaN, the interface thickness can be controlled below

1.5 nm, resulting in ultra-low thermal resistance and stable electrical performance. If Ra exceeds 1 nm, micro-voids form at the interface, increasing thermal resistance and raising interface state density to

~10¹³ cm⁻²·eV⁻¹, severely degrading electrical performance.

Thickness non-uniformity beyond

0.2 µm leads to uneven bonding pressure and local bonding failure. Films deposited under high carbon concentration require additional polishing, increasing the risk of film damage and delamination.

Key advantages:

Well suited for

ultra-thin heat spreaders, flexible devices, microwave and optoelectronic applications, provided deposition efficiency and surface smoothness are carefully balanced.

3. Wafer Bonding Compatibility Strategies and Surface Optimization Directions

3.1 Surface Quality Requirements by Bonding Technology

Surface-Activated Bonding (SAB)Ra ≤ 0.5 nm (vacuum-sealed interfaces) or ≤ 1 nm (general use)

TTV ≤ 3 µm, Warp ≤ 25 µm

Argon beam energy: 1–2 kV to avoid over-etching

Post-bond annealing at 300–400°C removes amorphous layers; 1000°C annealing can reduce interface state density to one-fifth.

Hydrophilic BondingSimilar Ra requirements (< 1 nm)

Requires uniform OH termination; rough surfaces trap moisture and create voids

Limited adoption in diamond bonding due to water desorption challenges.

Atomic Diffusion BondingSlightly more tolerant to flatness

Requires Ra < 2 nm

Intermediate layers (amorphous Si, Al₂O₃) help fill micro-defects and enhance bonding strength.

3.2 Surface Process Optimization Trends

Single-Crystal Diamond:

Development of high-efficiency, low-damage CMP slurries and optimized laser trimming parameters.

Polycrystalline Diamond:

Breakthroughs in full-area polishing for large wafers, grain orientation control, and stress-buffer layer design.

Diamond Films:

Optimized CVD parameters (CH₄/H₂ ratio, argon dilution) to integrate deposition and initial planarization while improving film adhesion.

4. Conclusion

Surface flatness and roughness are

critical determinants of wafer bonding success for diamond substrates, influencing every stage from surface activation and pressure application to interface formation and thermal stability.

Single-crystal diamond excels in high-precision, high-performance bonding.

Polycrystalline diamond requires breakthroughs in large-area flatness control.

Diamond films demand coordinated optimization of thickness uniformity and surface smoothness.

Future progress will rely on

advanced surface processing technologies, such as high-efficiency polishing and precision CVD control, combined with

bonding process innovations including buffer layer engineering and optimized annealing. These advances will significantly reduce cost barriers and accelerate the

large-scale adoption of diamond substrates in heterogeneous semiconductor integration and thermal management applications.