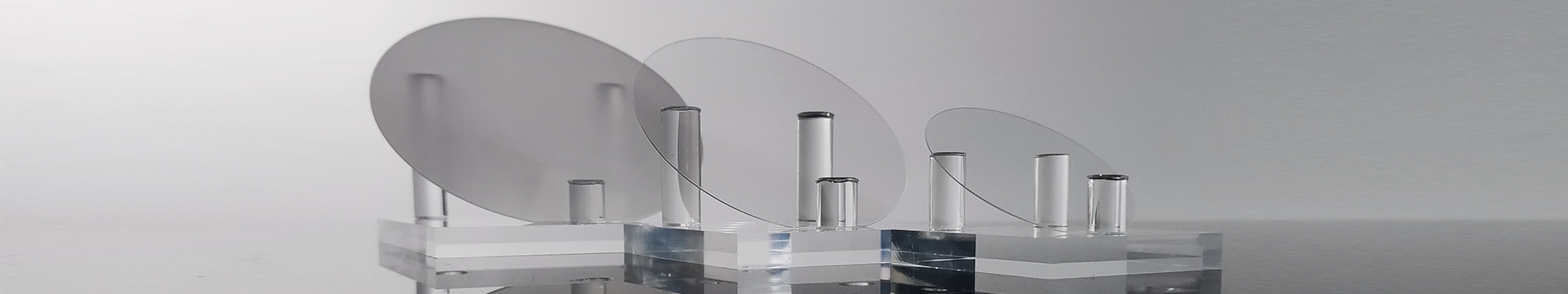

The 8-inch N-type SiC double-side polished substrate is a silicon carbide wafer with a diameter of 8 inches (approximately 200 millimeters), processed through double-side polishing to achieve high flatness and smoothness, utilized in the manufacturing of high-power electronic devices such as power MOSFETs, Schottky diodes, and high-frequency RF devices due to its excellent material properties for efficient and reliable applications.

Specifications of 8 inch N-type SiC Double-side Polished Substrate

| Items | Unit | Ultra-P |

Production | Dummy | |||||

| Boule Parameters | |||||||||

| Polytype | -- | 4H | |||||||

| Surface orientation error | 。 | 4°toward<11-20>±0.5° | |||||||

| Electrical Parameters | |||||||||

| Dopant | -- | n-type Nitrogen | |||||||

| Resistivity | ohm.cm | 0.015~0.025ohm.cm NA | |||||||

| Mechanical Parameters | |||||||||

| Diameter | mm | 200.0±0.2mm | |||||||

| Thickness | μm | 350/500±25μm | |||||||

| Notch orientation | 。 | [1-100]±5 | |||||||

| Notch Depth | mm | 1~1.5mm | |||||||

| LTV | μm | ≤3μm(10mm*10mm) | ≤5μm(10mm*10mm) | ≤15μm(10mm*10mm) | |||||

| TTV | μm | ≤7μm | ≤10μm | ≤20μm | |||||

| Bow | μm | -20μm~20μm | -25 μm~25μm | -65μm~65μm | |||||

| Warp | μm | ≤30μm | ≤35μm | ≤70μm | |||||

|

Front(Si-face)Roughness(AFM) |

nm | Ra≤0.2nm | |||||||

| Structure | |||||||||

| Micropipe density | ea/cm² | <0.2ea/cm² | <2ea/cm² | ≤50ea/cm² | |||||

| Metal impurities | atoms/cm | ≤1E11atoms/cm²(Al, Cr, Fe,Ni, Cu, Zn, Pb, Na, K, Ti, Ca,V, Mn) | |||||||

| TSD | ea/cm² | ≤200ea/cm² | ≤500ea/cm² | NA | |||||

| BPD | ea/cm² | ≤1000ea/cm² | ≤2000ea/cm² | NA | |||||

| TED | ea/cm² | ≤3000ea/cm² | ≤7000ea/cm² | NA | |||||

| Front Quality | |||||||||

| Front | Si | ||||||||

|

Surface Finish |

Si - CMP Si-face CMP | ||||||||

| Particles | ea/wafer | ≤60(size≥0.3μm) | ≤100(size≥0.3μm) | NA | |||||

| Scratches | ea/mm | <5,Totallength≤1/2*Diameter | <5,Totallength≤Diameter | NA | |||||

| Edge chips/indents/cracks/stains/contamination | -- | None | |||||||

|

Polytype area |

-- | None | |||||||

|

Front laser marking |

-- | None | |||||||

| Back Quality | |||||||||

| Back finish | -- | C-face polished | |||||||

| Scratches | ea/mm | ≤5,Total Length≤Diameter | |||||||

| Back defects (edge chips/indents) | -- | None | NA | ||||||

| Back roughness | nm | Ra≤5nm | |||||||

|

Back laser marking |

-- | Notch | |||||||

| Edge | |||||||||

| Edge | -- | Chamfer | |||||||

| Packaging | |||||||||

| Packaging | -- | Epi-ready with vacuum packaging | |||||||

| Packaging | -- | Multi-wafer or single wafer cassette packaging | |||||||

As an outstanding supplier of silicon carbide substrates, JXT TECHNOLOGY is committed to providing high-quality SiC materials.With advanced manufacturing processes and stringent quality control standards, we ensure our products exhibit excellent flatness and surface smoothness. As a supplier of silicon carbide materials, we focus on meeting customer demands and providing crucial support to the high-power electronic device manufacturing industry.

As the third-generation wide-bandgap semiconductor industry develops rapidly, 4H-semi-in...

Abstract: Gallium Nitride (GaN), a core third-generation wide-bandgap semiconductor, is ...

The core requirements of RF devices (such as 5G/6G base station power amplifiers, satell...