As the core material of third-generation wide-bandgap semiconductors, silicon carbide (SiC) is essential in high-performance semiconductor fields like new energy vehicles, AI computing power, and photovoltaic energy storage due to its superior electrical and thermal properties. Epitaxial growth is critical for SiC device fabrication, as its quality directly determines device performance. With semiconductors evolving toward high power and large sizes, SiC epitaxial growth encounters multiple technical bottlenecks. This paper analyzes these key challenges and proposes targeted solutions to support industrial application.

I. Core Technical Background of SiC Epitaxial Growth

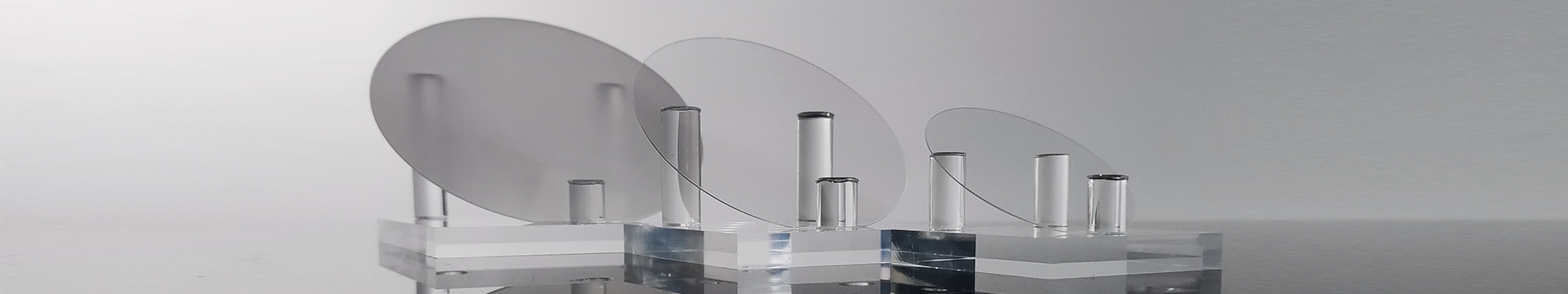

SiC epitaxial growth involves depositing a lattice-matched, high-quality SiC thin film on a high-purity substrate, typically performed at 1500-1700℃ in an inert gas or high-vacuum environment. Chemical Vapor Deposition (CVD) is the mainstream technology, favored for its strong process controllability and industrial adaptability.

The popularization of 800V automotive architectures and rising AI chip power consumption have raised requirements for SiC epitaxial layer uniformity, doping precision, and defect density. Core challenges include defect control, large-size adaptation, process stability, and cost control.

II. Key Challenges of SiC Epitaxial Growth

(1) Difficulties in Crystal Defect Control

Crystal defects are the primary limitation to epitaxial quality and device reliability. High-performance semiconductors demand extremely low defect density, but three main defects occur during growth: substrate-derived basal plane dislocations (BPD) and threading edge dislocations (TED) — BPD can extend to form stacking faults (SF), degrading bipolar devices; process-induced defects (e.g., point defects) from temperature fluctuations or gas imbalance; and stress-induced cracks from lattice/thermal expansion mismatches between the epitaxial layer and substrate.

While 6-inch epitaxial layers have low defect density, 8-inch and larger layers struggle to reach the 0.5 cm⁻² threshold. Traditional defect control requires a 5-10μm high-nitrogen buffer layer, shortening equipment life and affecting drift layer concentration control.

(2) Poor Uniformity of Large-Size Epitaxial Layers

SiC substrates are advancing from 6-inch to 8-inch and 12-inch to reduce costs, but this complicates uniformity control. Uneven temperature and gas flow in the reaction chamber cause varying growth rates and doping adsorption across the substrate. For 8-inch layers, thickness uniformity often exceeds 3% and doping fluctuation exceeds 7.5%, failing device consistency requirements. Surface scratches or contamination on large substrates worsen these issues, reducing mass production yield.

(3) Unstable High-Temperature Processes

High-temperature operation (1500-1700℃) causes process instability: chamber and graphite susceptor wear generates impurities; precursor cracking efficiency is sensitive to temperature (a >5℃ deviation degrades growth quality); improper cooling intensifies internal stress and cracking, especially for large sizes. Traditional equipment’s poor temperature control and airtightness lead to batch differences, lowering mass production yield.

(4) High Costs Hinder Industrialization

High-performance SiC epitaxy is more costly than silicon epitaxy: high-purity precursors and inert gases have only 30%-50% utilization; core equipment relies on imports with high purchase/maintenance costs; low large-size yield and heavy R&D investment, plus domestic technical bottlenecks, keep epitaxial layer costs high, limiting large-scale application in mid-to-low-end devices.

III. Targeted Solutions

(1) Optimizing Defect Control

A full-process approach — substrate pretreatment, process optimization, and defect repair — reduces defect density. Pretreatment uses high-temperature nitrogen ion implantation to convert BPD to TED, combined with Chemical Mechanical Polishing (CMP) and plasma cleaning. The high-nitrogen buffer layer is simplified to 0.2-0.5μm; CVD parameters (±2℃ temperature accuracy, Si/C ratio 1.0-1.2) and Microwave Plasma CVD (MPCVD) improve quality. 1600-1700℃ annealing and 5-10℃/min gradient cooling relieve stress and repair defects.

(2) Ensuring Large-Size Uniformity

Uniformity is achieved via three measures: improved CVD chambers with zoned heating and annular gas injection, plus plasma enhancement (China’s 8-inch epitaxy now has ≤2.3% thickness uniformity and <7.5% doping fluctuation); real-time closed-loop control, substrate rotation to reduce edge effects, and 1-5μm/h growth rate; high-precision CMP to control substrate roughness below 0.1nm and reduce stress.

(3) Enhancing High-Temperature Stability

Stability is improved by using high-temperature/corrosion-resistant coatings, upgrading temperature control to ±1℃, and regular equipment maintenance. Domestic SiC MOCVD equipment (AMEC, NCMS) is replacing imports. Standardized processes, AI intelligent control, and batch traceability reduce errors. High-purity hydrogen protection and in-situ laser interferometer monitoring prevent batch defects.

(4) Reducing Costs

Costs are cut by optimizing raw material recovery (≥70% utilization) and developing low-cost precursors; promoting domestic equipment/materials (Xiamen University’s 8-inch breakthrough, Tianke Heda’s substrate-epitaxy integration); optimizing growth rate, expanding production scale, and adopting automatic detection to reduce labor and loss.

IV. Summary and Outlook

High-performance semiconductor development drives

SiC epitaxy toward high quality, large size, and low cost. Key challenges have seen partial breakthroughs, with 8-inch epitaxy maturity placing China among global leaders. Future focus will be on 12-inch epitaxy and ultra-low defect control, strengthening industry-university-research cooperation, advancing domestic equipment/materials, and promoting large-scale application to support energy and computing power revolutions.